二,

数字信号基础

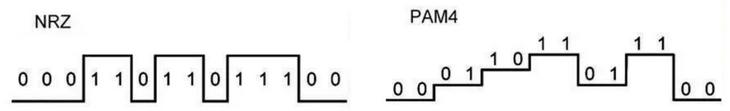

让我们的眼光先从总线层面移开,再向下一层看:数字信号(这章内容是整个总线专题的概念基础,非常重要)。总线的目的在于传输数据,而数据是由数字信号来呈现的,所以在本质上来说:系统中各个模块主要通过数字信号的传输来进行信息的交互。那么数字信号如何来表达其含义呢?典型的数字信号用两个不同的信号电平分别来代表逻辑“0”和逻辑“1”的状态。如下图所示。

——随着对数据传输速率需求的提升,也可以有4个不同的电平:

PAM4(4-Level Pulse Amplitude Modulation),来表示2bit逻辑状态:00,01,10,11。

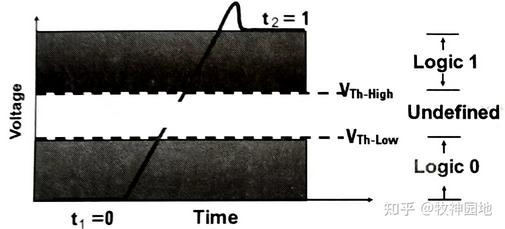

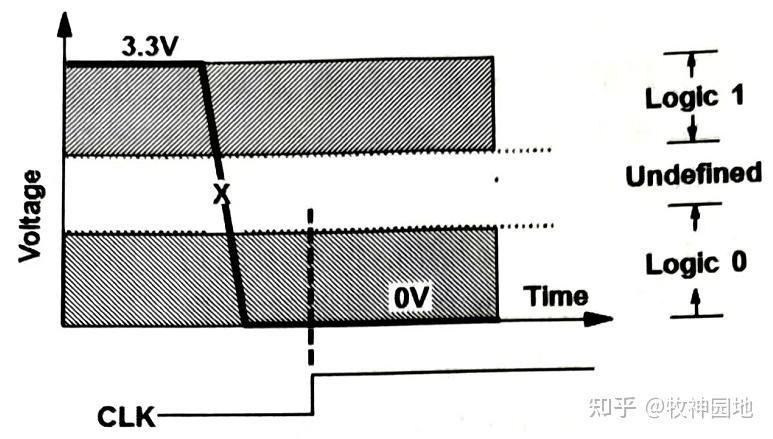

但是真实的世界并不存在理想的逻辑“0”和“1”的状态,所以只能用一定的信号电平电压范围来代表响应的逻辑状态,如下图所示。

——所谓的不确定状态是指:接收端可能将这个状态判决为逻辑0,也可能判决为逻辑1;是一种不受我们控制的状态(具体分析请参考《逻辑门电路高速特性》)。

1,数字信号的基本参数

通过上面的简单学习,我们了解了数字信号是个啥,大家一起接下去学习关于数字信号的基本参数;这些参数关系到了数字信号在总线中的应用,在接下去不同总线协议的电气规格中将不断出现。所以我们需要先去理解,这些参数背后代表了什么意义。

1.1 数字信号边沿时间

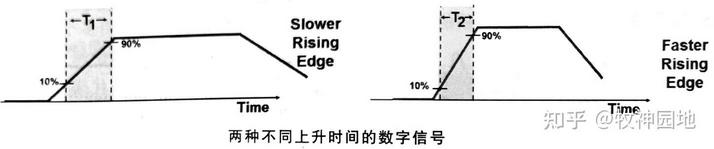

任何一个真实的数字信号从一个逻辑电平状态(比如:低电平)跳变到另一个逻辑电平状态(比如:高电平)时,其边沿时间都不会是0;而边沿跳变的过渡时间越短,则说明信号边沿越陡。我们一般用信号上升时间(Rising Time)来衡量信号边沿的陡缓程度,上升时间一般指:数字信号幅度由10%增加到90%所用的时间(或则从20%到80%所用的时间,根据不同器件规格设定);大多数数字信号的下降时间(信号幅度从90%下降为10%所用时间)同上升时间差不多。具体如下图所示。

上升时间可以客观地反映信号边沿的陡缓程度,对一些高速总线信号:

PCIe,USB3.0等,由于信号速率较高,传输线对信号的损耗很大(关于信号高频分量的损耗分析,具体参考《从电感、电容到理想传输线》章节相关内容),在信号波形中很难找到稳定的10%90%的位置,所以会用20%80%的边沿时间来衡量信号的陡缓程度。

那么信号边沿的陡缓程度跟什么相关呢?记性好的胖友应该还记得,在《从频域出发理解信号》章节的内容中我们分析过,数字信号的边沿时间决定了信号的带宽!

1.2 数字信号带宽

数字信号的带宽非常重要,它表示该数字信号所携带的高频能量信息,如果在传输过程中这部分高频能量信息被损耗掉,那么数字信号本身将会失真,从而导致接收端数据判决出错。所以在电路设计中,数字信号的带宽决定了PCB走线和介质的传输带宽要求,也决定了在信号测量中对仪器的带宽要求。

我们已经知道作为理想方波信号的高频分量是无穷的(集中在奇次谐波能量:1,3,5,7….次谐波);但是真实数字信号既不是理想方波,也不是正弦波,所以它的能量主要集中在一个频域范围之内,有很多高频谐波成分(1,2,3,4,5….次谐波)。

——需要特别注意的是:理想方波的高频谐波能量主要集中在奇次谐波上,而真实数字信号谐波主要集中在倍频上(包括偶次谐波);所以并非所有数字信号的高频分量奇次谐波的能量大,具体原理在这里不做分析,具体后续《电磁兼容性基础》中进行数学模型分析。

- 基于上升沿时间的信号带宽计算:我们通常根据数字信号上升沿去估算被测信号的频谱能量,信号最高频率分量 = 0.5/信号上升时间(10%

90%);如果使用20%80%的上升时间标准时,计算公式为:信号最高频率分量 = 0.4/信号上升时间(20%~80%)。

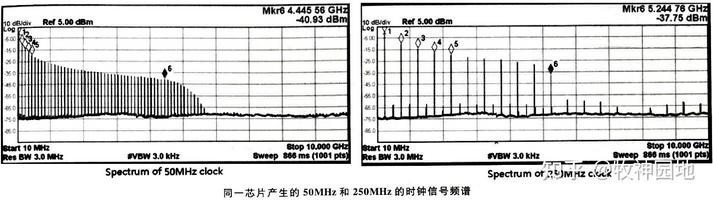

——这种估算方法相对更加准确,在《从频域出发理解信号》章节中的数字信号带宽估算公式是:信号最高频率分量 = 0.35/信号上升时间(注意:由于这只是一种估算的方法,所以不同的参考资料会有不同的系数。);当然想要获得信号能量的频率分布最准确的方法是:使用频谱分析仪对被测数字信号进行分析。

1.3 数字信号的建立/保持时间

建立/保持时间对总线通信非常重要,因为在信号跳变时总会有一段过渡时间处于逻辑的不确定状态;而很多总线信号并不只有一路,会有多路信号同时传输,而不同路的数字信号的电气特性不可能完全一致(PCB损耗,走线延时等等),所以当不同信号到达接收端时会存在不同的时延,这样更增加了逻辑状态不确定的时间。

我们期望接收到的数字信号是稳定的状态,而非跳变时的状态,所以大部分数字电路采用了同步电路,即系统总有一个统一的工作时钟对信号进行采样。如下图所示,虽然在信号跳变过程中存在不确定状态,但是在时钟CLK上升沿时对信号进行判决采样,得到的是稳定的逻辑状态。所以,采用同步时钟的电路减小了逻辑不确定状态的概率,而且减小了电路和信号走线延时的积累效应;这种数字电路以固定的时钟节拍工作,我们将数字信号每秒钟跳变的最大速率称作信号的数据速率(Bit Rate),单位是bps(Bits Per Second)或bit/s。大部分并行总线的数据速率和总线系统时钟的工作频率是一致的(有一种特殊情况:DDR总线的数据速率是时钟频率的2倍),一些高速传输总线(PCIe,USB3.0等),时钟信息是通过编码嵌入在数据流中,虽然我们看不到有单独的时钟传输通道,但其工作仍然有特定的数据速率。

——我们在后续《PCIe总线基础》专题中扩展分析。

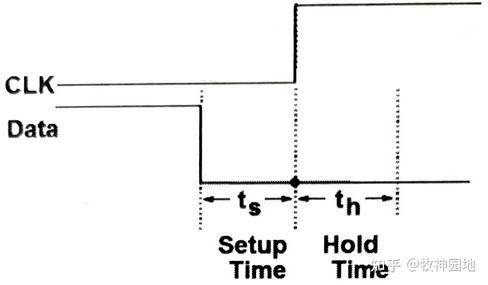

但是在同步电路中如果要想得到稳定的逻辑状态,对采样时钟和数据信号之间的时序是有要求的;举个栗子,如果时钟上升沿正好对着数据信号的跳变区域附近,就可能采样到不稳定的逻辑状态。所以为了得到稳定的逻辑状态,通常要求如下图所示;

- 建立时间(ts)和保持时间(th)时间加起来的时间称作:建立/保持时间窗口;这是接收端对于信号要保持同一个路基状态的最小时间要求,如果数字信号的bit宽度小于建立/保持时间窗口,数据信号就不可能同时满足建立时间和保持时间的要求,所以接收端对于建立/保持时间的窗口大小,实际上决定了电路能够工作的最高数据速率。另外,输出端的信号边沿的陡缓,输出信号幅度偏小,信号和时钟的抖动以及信号有畸变等因素都会使得建立时间和保持时间变小,所以最高数据传输速率与发送芯片和接收芯片以及走线都有关。

——一般情况下工作速率高的器件,只需要很小的建立时间和保持时间就可以保证电路可靠工作了,而工作速率低的器件则要求比较长的建立时间和保持时间。

——建立/保持时间是总线时序设计的最基本要求,是总线可靠工作的基础。

2,并行总线与串行总线

虽然现在数字芯片的功能集成度越来越高,举个栗子:手机处理器集成了DRAM,Flash,GPU等等,但只要需要与外界有信息交互(与外界没有任何信息交互的系统是没有用处的),则必然需要总线来实现该芯片与其它功能模块之间的互连。而根据数据传输方式的不同,可以将总线分为:并行总线和串行总线。

2.1 并行总线

并行总线是数字电路总最普遍采用的总线,这类总线要传输数据线、地址线、控制线等等(并行传输);举个栗子:如果传输8bit数据宽度,那么需要8根数据信号线;除此之外,如果要寻址不同的地址空间需要很多根不同的地址线的组合来代表不同的地址。典型代表是多年前非常常用的

LocalBus,如下图所示。并行总线最大的好处是:总线逻辑时序比较简单,电路实现相对比较容易;但它的缺点也非常明显:信号线数量太多,占用大量的管脚和布线空间,器件以及PCB板尺寸难以实现小型化。

对于并行总线来说提升数据传输速率有两种方法:1,提升数据线位数(8bit,16bit,32bit,64bit);2,提升数据速率(133Mbps,266Mbps,533Mbps等)。总线吞吐量 = 数据线位数 x 数据速率。以PCI总线为例,其最早推行的工作时钟是33MHz,数据线位数是32bit;后来为了提升总线速率,将数据宽度扩展到64bit,工作频率提升到133MHz;此时总线吞吐量 = 133MHz * 64bit ≈1GBps;但是随着人们对总线吞吐量更高的要求,并行总线的方式遇到了很大瓶颈:

2.2 串行总线

为了解决并行总线的这些问题:占空器件和PCB尺寸过大,总线吞吐量受限等等。随着芯片技术的发展和速度的提升,越来越多的数字接口开始采用串行总线。串行总线指的是:并行的数据在总线上不再是并行的传输,而是分时复用在一根或几根信号线传输。举个栗子:并行总线传输8bit的数据宽度需要8根数据线,而将这8根信号线上的数据分时复用到一根信号线上,就可以大大减少信号线数量,也不需要考虑信号线之间的等长关系。

——采用串行总线后,单根信号线上要传输原来多根(8,16,32根等)信号线上的数据,所以串行总线信号速率相应的要比并行总线速率要高很多;举个栗子:PCI总线上单根信号速率是133Mbps,而PCIe总线上单根信号速率是2.5Gbps,5Gbps和8Gbps。

串行总线数据速率提高了之后,必然带来了更严峻的信号完整性问题;对于传输线的阻抗连续性(阻抗匹配),线路损耗和抖动的要求更高了,如果不加注意就很容易产生信号质量问题。所以高速串行总线的设计对于硬件工程师来说是一个重大的挑战。

2.3 单端与差分信号

我们已经学习了《电平设计基础》,在该专题中详细地介绍了单端与差分信号。

单端信号是指:用一根信号线的高低电平变化来进行0,1数据的传输,该高低变化是相对于公共参考地平面的。单端信号的输入/输出结构简单(如TTL/CMOS)、集成度高、功耗较低,所以在数字电路中有非常广泛的应用。

随着信号传输速率的增加,为了减小信号跳变时间和功耗,信号幅度需要不断的减小;因为信号幅度减小意味着对信号边沿斜率要求的降低,就不需要那么强的电流驱动能力了;举个栗子,3.3V电压幅度的边沿时间是10ns,那么其边沿斜率是0.33V/ns,而1.2V电压幅度边沿时间是10ns,其边沿斜率是0.12V/ns,电流驱动能力线性减小。所以我们看到单端信号的电平的发展趋势是越来越低:3.3V2.5V1.8V1.5V1.2V。

——信号跳变时间(边沿时间)小,那么数据速率才能提高;根据负载的RC充电模型(具体参考《逻辑门电路高速特性》相关章节),在相同幅度下越小的边沿时间,那么需要更大的电流驱动能力(功耗更大);举个栗子:1MHz的3.3V幅度信号,边沿时间按照10%周期计算是100ns,而100MHz的边沿时间则是1ns;那么如何能将边沿时间从100ns提升至1ns么?就需要更强的驱动电流,使得信号电平快速抬升。

然而信号幅度的减小所带来的问题是噪声容限的降低,信号线传输距离受到限制,对传输线的阻抗设计要求越来越高,而且更容易受到串扰的影响。单端信号电平很难再更低下去了,同时说明单端数据传输速率也很难得到更大的提升。而解决方案,胖友们都已经知道了:差分信号。

差分信号是指:用一对反向差分线进行信号传输,发送端采用差分的发送器,接收端采用差分的接收器。它保证了数据在高速率、长距离下的可靠传输。

——但基于上述的这么多优点,差分传输方式得到了非常广泛的应用:PCIe,SAS,SATA,USB、SGMII、GE等等。

2.4 总线时钟

上面说了,我们目前的总线大部分采用的同步时钟,总线数据的可靠传输依赖于准确的时钟采样。一般情况下发送端和接收端都需要使用相同频率的工作时钟(接口时钟)才能保证数据不丢失。总线采用的时钟分配方式大致分为三类:并行时钟,嵌入式时钟,前向时钟;

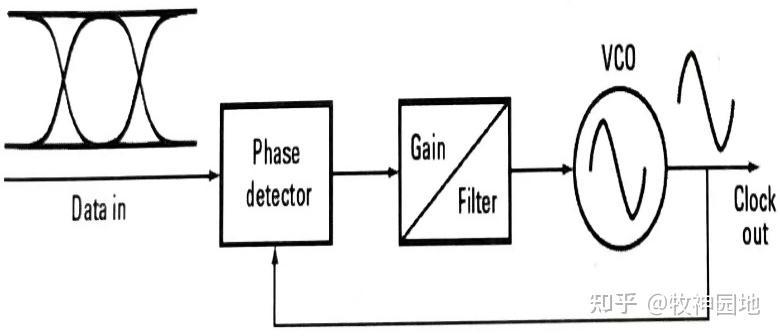

(1)CDR中的PLL电路能够很好地跟踪上数据中低频抖动,所以适合长距离传输; ——低频抖动是数据速率的缓慢变化,该变化的频率低于环路滤波器的带宽,则输入信号抖动造成的相位变化信息就可以通过环路滤波器,从而调整VCO输出频率。 ——恢复出来的时钟和被测信号一起抖动(同步抖动),所以时钟相对于信号(时钟采样信号)的建立/保持时间不会有太大的影响。 (2)CDR由于受到环路滤波器带宽的影响,高频抖动会被PLL电路过滤掉,因此恢复的时钟中不包含这些高频的抖动成分,所以数据线上的高频抖动会对接收端采样产生较大的影响。 ——输入信号中抖动的频率较高,其造成的相位变化信号不能通过环路滤波器,则VCO输出时钟中就不会有随输入信号一起变化的抖动成分。 ——恢复时钟没有高频抖动而信号存在这些高频抖动,所以信号相对于时钟的建立/保持时间会有很大的影响。 4, 嵌入式时钟的缺点是:增加了电路复杂度,而且数据编码导致降低了总线效率。 ——举个栗子:8b/10b编码的数据传输效率是80%;那么5Gbps速率的总线数据中只有4Gbps是有效数据。

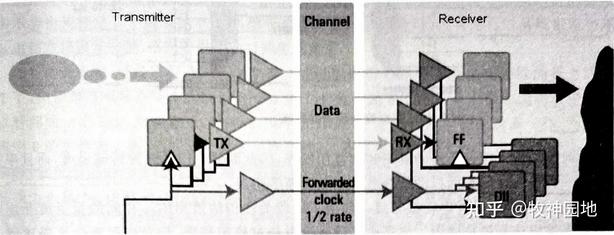

- 前向时钟:对总线吞吐率和效率要求更高的应用,采用的新时钟分配方式,它得益于DLL(Delay Locked Loop)电路,它最大的好处是可以很方便地用成熟的CMOS工艺大量集成而且不会增加抖动;如下所示为前向时钟的典型应用:总线有单独的时钟传输通道,而不同的是内部有DLL电路,其工作时可以有一个训练的过程,接收端DLL在训练过程中根据每条数据信号线的时延情况调整时延,从而保证每条数据线都有充分的建立/保持时间。

——

DDR DRAM的CLK与DQS之间采用的是DLL同步方式,而DQS与DQ之间是要求保持精确等长,属于前向时钟的一种,后续在《DDR DRAM总线基础》中再来详细介绍。另外还有

QPI总线等等。

1, 前向时钟总线因为有专门的时钟通道,不需要对数据进行编解码,所以总线效率更高;

2, 线路噪声和抖动对于时钟和数据线的影响是一样的(一般在同层、同区域走线),所以系统的影响可以消除;

——对高频抖动的敏感度相对于嵌入式时钟要小很多。

2.5 串行总线编码

串行总线在高速链路传输中对并行总线具有压倒性的优势,但是一般CPU/DSP/FPGA等内部跑的还是并行总线(32bit/64bit/128bit等),数据处理的最小单位是Byte,那要将一个或多个byte的数据通过串行的方式传输出去,必须要对数据做特殊处理。

最简单的方式是:发送端的并行数据直接转换成串行数据发出去。举个栗子:位宽为8bit,速率为100Mbps的数据,通过Mux芯片将8bit数据时分复用到1bit的数据线上,相应的数据速率提高到800Mbps,当数据信号到达接收端后,再通过De-Mux芯片将串行信号分成8路低速数据。这种串并转换的方法不涉及信号编解码,结构简单、效率较高,但需要精确的时钟同步以控制信号的串并转换,所以需要专门的时钟传输通道,一旦出现较大的抖动则会造成串并转换的错误。而且这种简单的串并转换方式,由于没有经过任何编码,信号中会出现较长的连续0或1,因此信号需要采用直流耦合的方式(直流平衡点根据数据会发生变化),对共模噪声比较敏感。

——这种没有经过任何编码的并串转换,适用于短距离的高速互连。

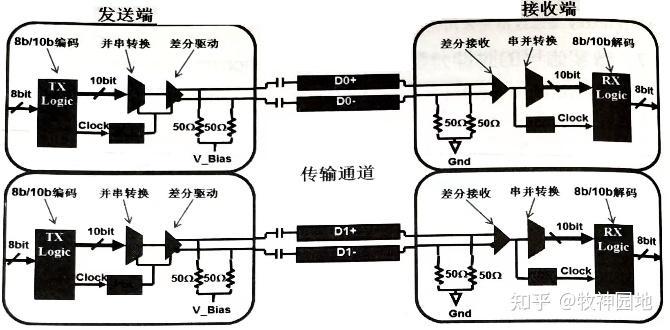

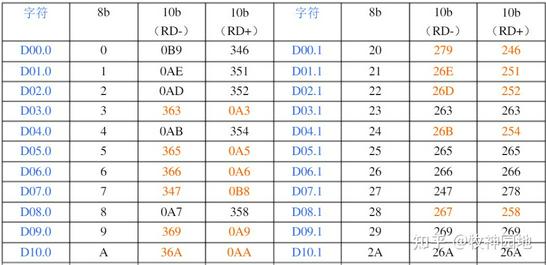

目前大多高速串行数字接口采用的是先编码再做串并转换的方式,编码方式如上所述有很多种;我们以8b/10b为例来进行介绍。8b/10b编码就是:8bit的数据先通过相应的编码规则转换成10bit的数据;因此,如果原始数据速率是800Mbps,那么物理链路上的串行数据速率就是1Gbps。8b/10b编码方法最早由IBM发明,后来称为ANSI标准的一部分,在通信和计算机总线上得到广泛的应用。经过8b/10b编码后有几个最大的好处:

8bit原始数据对应有256种组合,那么每个原始数据对应2种10bit编码则有512种组合,而10bit理论上有1024种组合,所以有很多组合是无效的数据,这样当接收端收到这种无效组合数据时就可以判决数据无效,有利于数据的检验; ——这种数据检验只是简便的方法,最终还是需要通过协议上的CRC校验来实现数据有效性的检验。

10bit数据表示的1024个组合中,特殊的组合数据可以用来作为控制字符,代表特殊的含义,在初始化或数据包头进行发送;举个栗子:K28.5码型(后续《PCIe总线基础》中详细介绍)。

8b/10b编码最大的缺点在于编码过程中造成了20%的编码开销(有用数据只占到传输数据的80%),所以对更高速的传输来说这个开销就太大了,所以PCIe 3.0就采用了128b/130b的编码方式(开销更小),结合更加复杂的扰码方法来实现直流平衡和嵌入式时钟。

关于博主

an actually real engineer

通信工程专业毕业,7年开发经验

技术栈:

精通c/c++

精通golang

熟悉常见的脚本,js,lua,python,php

熟悉电路基础,嵌入式,单片机

耕耘领域:

服务端开发

嵌入式开发

>gin接口代码CURD生成工具

sql ddl to struct and markdown,将sql表自动化生成代码内对应的结构体和markdown表格格式,节省宝贵的时间。

qt .ui文件转css文件

duilib xml 自动生成绑定控件代码

协议调试器

基于lua虚拟机的的协议调试器软件 支持的协议有:

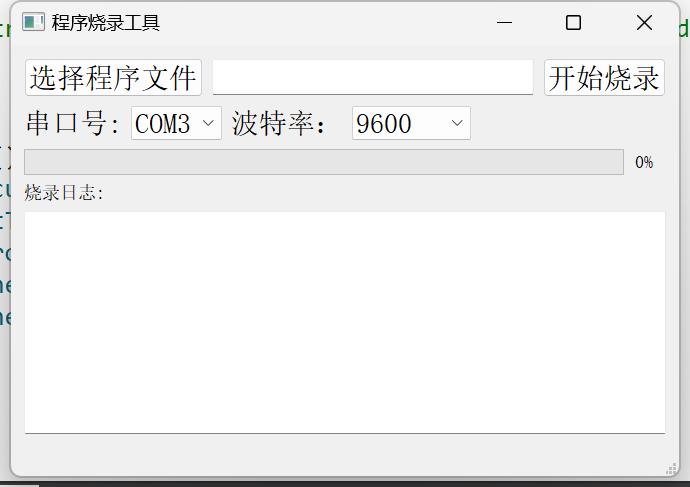

串口

tcp客户端/服务端

udp 组播/udp节点

tcp websocket 客户端/服务端

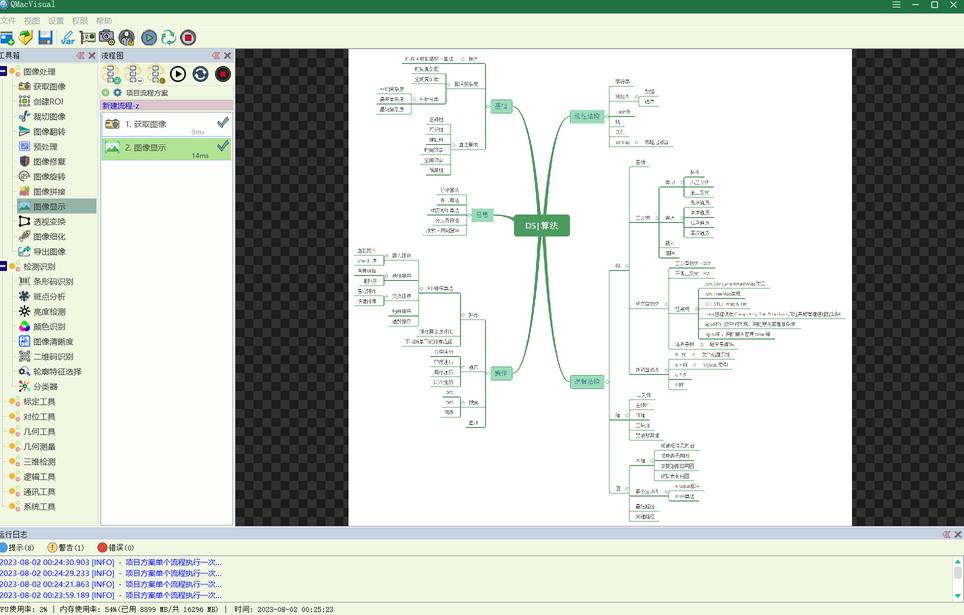

软件界面

使用例子: 通过脚本来获得接收到的数据并写入文件和展示在界面上

下载地址和源码

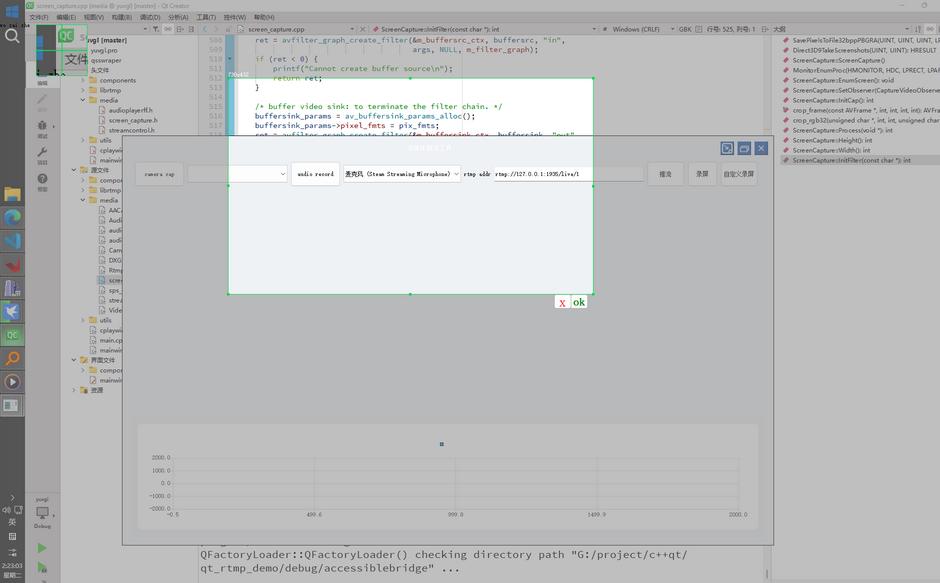

webrtc easy demo

webrtc c++ native 库 demo 实现功能:

基于QT

webrtc摄像头/桌面捕获功能

opengl渲染/多播放窗格管理

janus meeting room

下载地址和源码

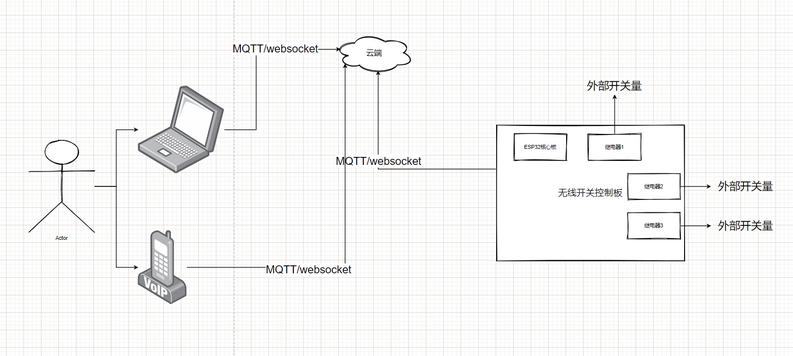

wifi,蓝牙 - 无线开关

实现功能:

通过wifi/蓝牙实现远程开关电器或者其他电子设备

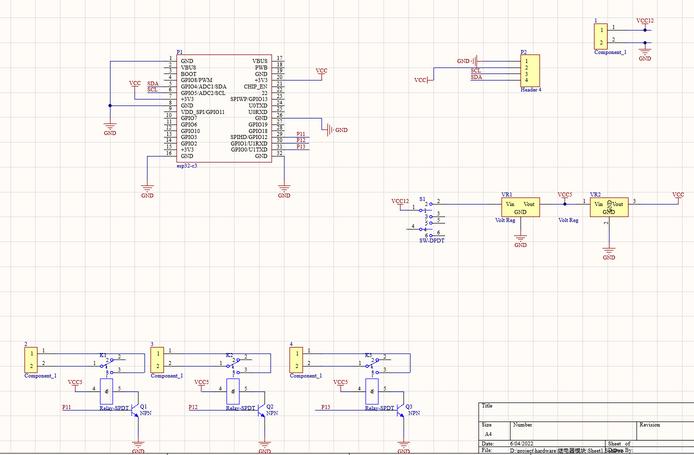

电路原理图:

实物图:

深度学习验证工具

虚拟示波器

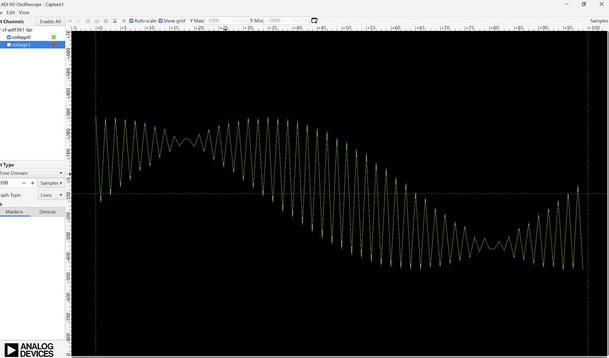

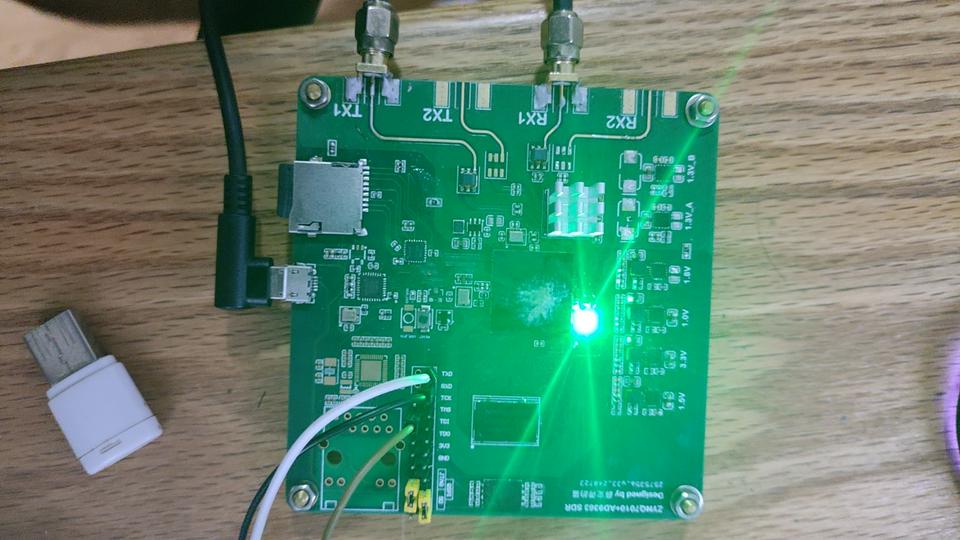

硬件实物图:

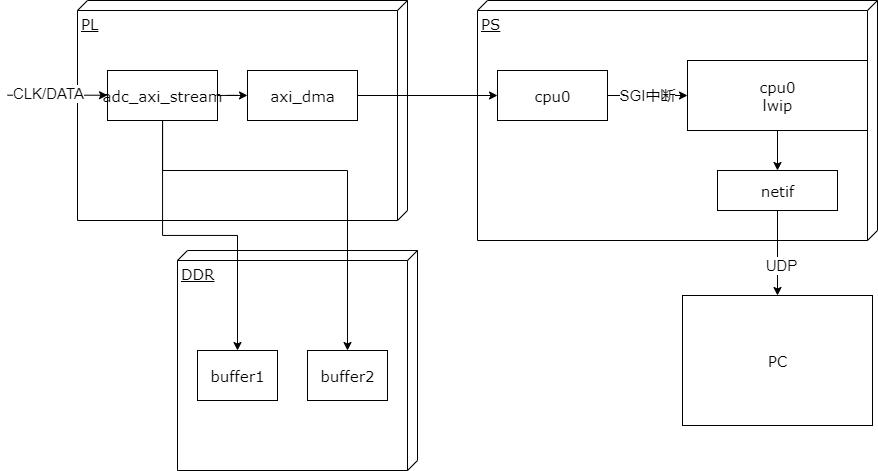

实现原理

基本性能

采集频率: 取决于外部adc模块和ebaz4205矿板的以太网接口速率,最高可以达到100M/8 约为12.5MPS

上位机实现功能: 采集,显示波形,存储wave文件。

参数可运行时配置

上位机:

显示缓冲区大小可调

刷新率可调节

触发显示刷新可调节

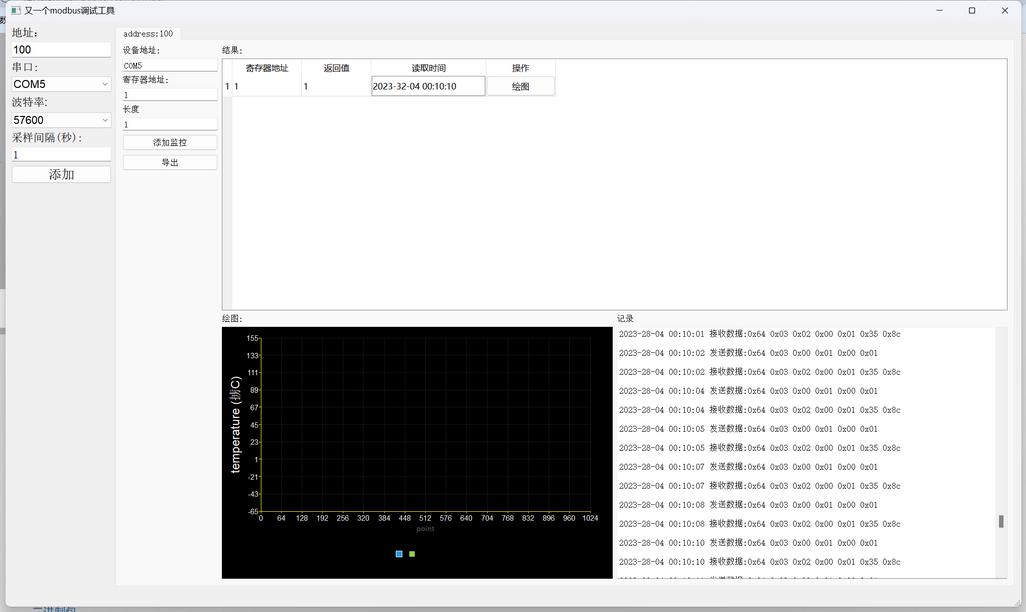

又一个modbus调试工具

最近混迹物联网企业,发现目前缺少一个简易可用的modbus调试工具,本软件旨在为开发者提供一个简单modbus测试工具。

主打一个代码简单易修改。

特点:

1. 基于QT5

2. 基于libmodbus

3. 三方库完全跨平台,linux/windows。

开源plutosdr 板卡

1. 完全开源

2. 提高固件定制服务

3. 硬件售价450 手焊产量有线

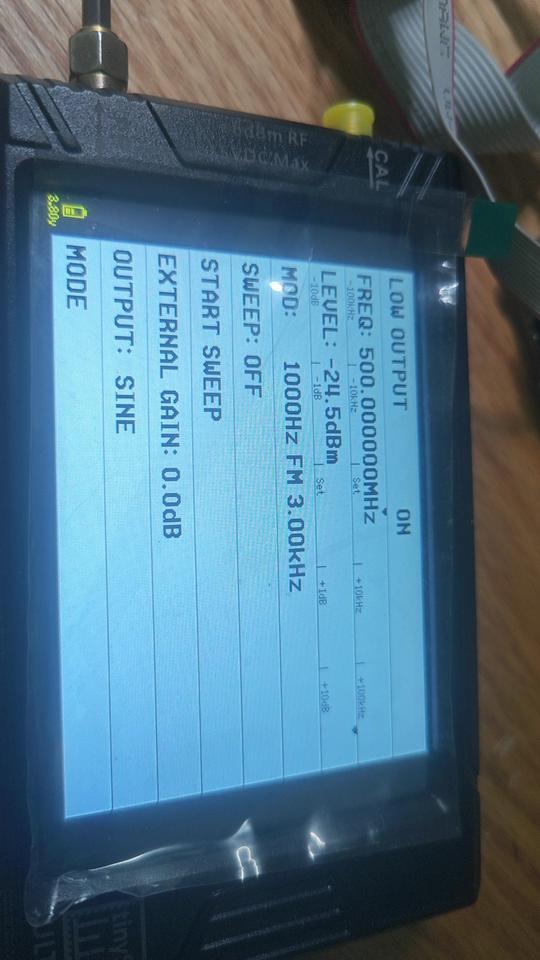

测试数据

内部DDS回环测试

接收测试

外部发送500MHZ FM波形

matlab测试

2TRX版本

大部分plutosdr应用场景都是讲plutosdr板卡作为射频收发器来使用。

实际上plutosdr板卡本身运行linux 操作系统。是具有一定脱机运算的能力。

对于一些微型频谱检测,简单射频信号收发等应用完全可以将应用层直接实现在板卡上

相较于通过网卡或者USB口传输具有更稳定,带宽更高等优点。

本开源板卡由于了SD卡启动,较原版pluto支持了自定义启动应用的功能。

提供了应用层开发SDK(编译器,buildroot文件系统)。

通过usb连接电脑,经过RNDIS驱动可以近似为通过网卡连接

(支持固件的开发定制)。

二次开发例子

```

all:

arm-linux-gnueabihf-gcc -mfloat-abi=hard --sysroot=/root/v0.32_2trx/buildroot/output/staging -std=gnu99 -g -o pluto_stream ad9361-iiostream.c -lpthread -liio -lm -Wall -Wextra -lrt

clean:

rm pluto_stream

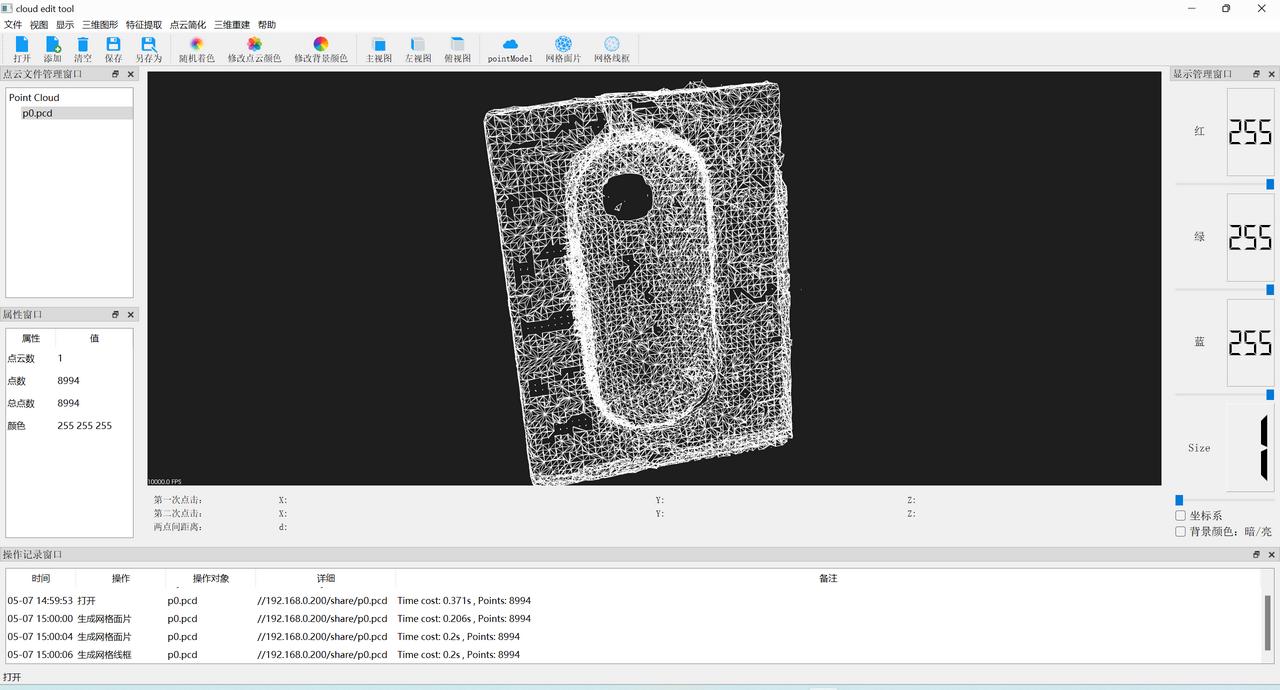

版面分析即分析出图片内的具体文件元素,如文档标题,文档内容,文档页码等,本工具基于cnstd模型